## 7110 1-MEGABIT BUBBLE MEMORY

| Device | Case Op.<br>Temp. °C | Non-Volatile<br>Storage °C |  |  |  |

|--------|----------------------|----------------------------|--|--|--|

| 7110-1 | 0-75°                | -40 to +90°                |  |  |  |

| 7110-4 | 10-55°               | -20 to +75°                |  |  |  |

| 7110-5 | -20 to +85°          | -40 to +100°               |  |  |  |

- 1,048,576 Bits of Usable Data Storage

- Non-Volatile, Solid-State Memory

- True Binary Organization: 512-Bit Page and 2048 Pages

- Major Track-Minor Loop Architecture

- Redundant Loops with On-Chip Loop Map and Index

- Block Replicate for Read; Block Swap for Write

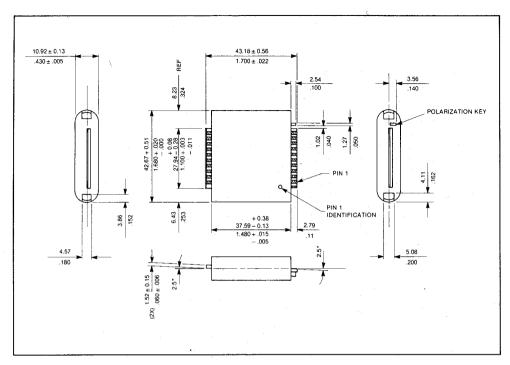

- Single-Chip 20-Pin, Dual In-Line Leadless Package and Socket

- Small Physical Volume

- Low Power per Bit

- Maximum Data Rate 100 Kbit/sec

- Average Access Time 40 msec.

The Intel Magnetics 7110 is a very high-density 1-megabit, non-volatile, solid-state memory utilizing magnetic bubble technology. The usable data storage capacity is 1,048,576 bits. The defect-tolerant design incorporates redundant storage loops. The gross capacity of Intel Magnetics bubble memory is 1,310,720 bits.

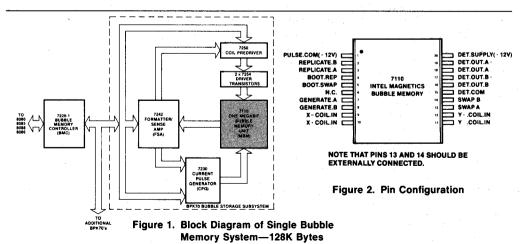

The 7110 has a true binary organization to simplify system design, interfacing, and system software. The device is organized as 256 data storage loops each having 4096 storage bits. When used with Intel Magnetics complete family of support electronics, the resultant minimum system is configured as 128K bytes of usable data storage. The support circuits also provide automatic error correction and transparent handling of redundant loops.

The 7110 has a major track—minor loop architecture. It has separate read and write tracks. Logically, the data is organized as a 512-bit page with a total of 2048 pages. The redundant loop information is stored on-chip in the bootstrap loop along with an index address code. When power is disconnected, the 7110 retains the data stored and the bubble memory system is restarted when power is restored via the support electronics under software control.

Intel Corporation Assumes No Responsibility for the Use of Any Circuitry Other Than Circuitry Embodied in an Intel Product. No Other Circuit Patent Licenses are Implied © INTEL CORPORATION, 1982

| Table 1 | 1. | 7110 | Pin | Description |

|---------|----|------|-----|-------------|

|---------|----|------|-----|-------------|

| Symbol               | Pin    | Name and Function                                                                                                             |

|----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------|

| BOOT.REP             | 4      | Two-level current pulse input for reading the boot loop.                                                                      |

| BOOT.SWAP            | 5      | Single-level current pulse for writing data into the boot loop. This pin is normally used only in the manufacture of the MBM. |

| DET.COM              | 15     | Ground return for the detector bridge.                                                                                        |

| DET.OUT              | 16–19  | Differential pair (A+, A- and B+, B-) outputs which have signals of several millivolts peak amplitude.                        |

| DET.SUPPLY           | 20     | +12 volt supply pin.                                                                                                          |

| GEN.A and GEN.B      | 7, 8   | Two-level current pulses for writing data onto the input track.                                                               |

| PULSE.COM            | 1      | +12 volt supply pin.                                                                                                          |

| REPA and REPB        | 3, 2   | Two-level current pulses for replicating data from storage loops to output track.                                             |

| SWAP.A and SWAP.B    | 13, 14 | Single-level current pulse for swapping data from input track to storage loops.                                               |

| XCOIL.IN, X+.COIL.IN | 9, 10  | Terminals for the X or inner coil.                                                                                            |

| YCOIL.IN, Y+.COIL.IN | 11, 12 | Terminals for the Yor outer coil.                                                                                             |

The 7110 is packaged in a dual in-line leadless package complete with permanent magnets and coils for the in-plane rotating field. In addition, the 7110 has a magnetic shield surrounding the bubble memory chip to protect the data from externally induced magnetic fields.

The 7110 operating data rate is 100 Kbit/sec. The 7110 can be operated asynchronously and has start/stop capability.

### **FUNCTIONAL DESCRIPTION**

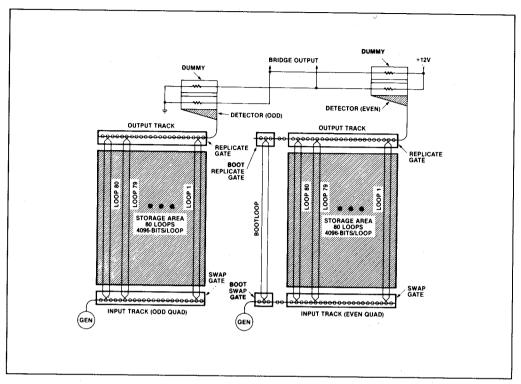

The Intel Magnetics 7110 is a 1-megabit bubble memory module organized as two identical 512K binary half sections. See Major Track-Minor Loop architecture diagram. Each half section is in turn organized as two 256K subsections referred to as quads.

The module consists of a bubble die mounted in a substrate that accommodates two orthogonal drive coils that surround the die. The drive coils produce a rotating magnetic field in the plane of the die when they are excited by 90° phase-shifted triangular current waveforms. The rotating in-plane field is responsible for bubble propagation. One drive field rotation propagates all bubbles in the device one storage location (or cycle). The die-substrate-coil subassembly is enclosed in a package consisting of permanent magnets and a shield. The shield serves as a flux return path for the permanent magnets in addition to isolating the device from stray magnetic

fields. The permenent magnets produce a bias field that is nearly perpendicular to the plane of the die. This field supports the existence of the bubble domains.

The package is constructed to maintain a 2.5 degree tilt between the plane of the bias magnet faces and the plane of the die. This serves to introduce a small component of the bias field into the plane of the die. During operation when the drive coils are energized, this small in-plane component is negligible. During standby or when power is removed, the small in-plane field ensures that the bubbles will be confined to their appropriate storage locations. The direction of the in-plane field introduced by the package tilt (holding field) is coincident with the 0° phase direction of the drive field.

#### **Quad Architecture**

A 7110 quad subsection is composed of the following elements shown on the architecture diagram.

## Storage Loops Fighty identical

Eighty identical 4096-bit storage loops provide a total maximum capacity of 327,680 bits. The excess storage is provided for two purposes: a) it allows a redundancy scheme to increase device yield; and b) it provides the extra storage required to implement error correction.

2) Replicating Generator (GEN)

The generator operates by replicating a seed

bubble that is always present at the generator site, (GEN).

- Input Track and Swap Gate Bubbles following generation are propagated down an input track. Bubbles are transferred to/from the input track from/to the 80 storage loops via series-connected swap gates spaced every four propagation cycles along the track. The swap gate's ability to transfer bubbles in both directions during an operation eliminates the overhead associated with removing old data from the loops before new data can be written. The swap gate is designed to function such that the logical storage loop position occupied by the bubble transferred out of each loop is filled by the bubble being transferred into each loop. Transferred-out bubbles propagate down the remaining portion of the input track where they are dumped into a bubble bucket guard rail.

- 4) Output Track and Replicate Gate Bubbles are read out of the storage loops in a nondestructive fashion via a set of replicate gates. The bubble is split in two. The leading bubble is retained in the storage loop and the trailing bubble is transferred onto the output track. Replicate gates are spaced every four propagation cycles along the output track.

- 5) Detector

Bubbles, following replication, are propagated along the output track to a detector that operates on the magneto-resistance principle. The cylindrical bubble domains are stretched into long strip domains by a chevron expander and are then propagated to the active portion of the detector. The detector consists of a stack of interconnected chevrons through which a current is passed. As the strip domain propagates through the stack, its magnetic flux causes a fractional change in stack resistance which produces an output signal on the order of a few millivolts. The strip domain following detection is propagated to a bubble bucket guard rail. A "dummy" detector stack sits in the immediate vicinity. It is connected in series with the active detector and serves to cancel common mode pickup which originates predominately from the in-plane drive field.

- 6) Boot Loop, Boot Swap, and Boot Replicate One of the two quads in each half chip contains a functionally active Boot Storage Loop. This loop is used to store:

- a) A loop mask code that defines which loops within the main storage area should be accessed. Faulty loops are "masked out" by the support electronics.

- b) A synchronization code that assigns data addresses (pages) to the data in the storage loops. Since bubbles move from one storage location to the next every field rotation, the actual physical location of a page of data is determined by the number of field rotations that have elapsed with respect to a reference.

The boot loop is read from and written into via the same input and output tracks as the main storage loops. However, it has independently accessed swap and replicate gates. The boot swap, under normal circumstances, is intended only to be used during basic initialization at the factory at which time loop mask and synchronization codes are written. The boot replicate is intended to be accessed every time power is applied to the bubble module and its peripheral control electronics. At such a time, the control electronics would read and store the mask information, plus utilize the synchronization information to establish the location of the data circulating within the loops.

Photo 1. 7110 Package Seated in Socket

Figure 3. Package Outline

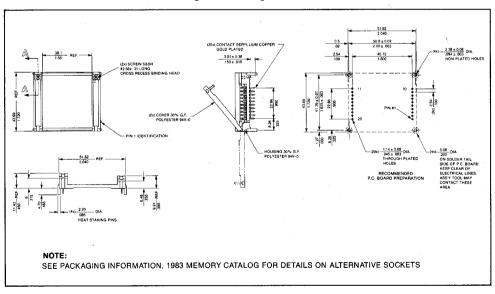

Figure 4. Socket Outline

AFN-01483B

Figure 5. Major Track-Minor Loop Architecture of 7110 (one half shown)

### **ABSOLUTE MAXIMUM RATINGS\***

| Operating Temperature20°C to +85°C Case Relative Humidity95% |

|--------------------------------------------------------------|

| Shelf Storage Temperature (Data                              |

| Integrity Not Guaranteed)65°C to +150°C                      |

| Voltage Applied to DET.SUPPLY 14 Volts                       |

| Voltage Applied to PULSE.COM 12.6 Volts                      |

| Continuous Current between DET.COM and                       |

| Detector Outputs                                             |

| Coil Current                                                 |

| External Magnetic Field for                                  |

| Non-Volatile Storage                                         |

| Non-Operating Handling Shock                                 |

| (without socket)                                             |

| Operating Vibration (2 Hz to 2 kHz                           |

| with socket)                                                 |

|                                                              |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **D.C. CHARACTERISTICS** ( $T_C$ = Range Specified on first page. $V_{DD}$ = 12V $\pm$ 5%)

|                                           | 71   | 10-1, -4 Lin        | nits | 7110-5 |       |       |

|-------------------------------------------|------|---------------------|------|--------|-------|-------|

| Parameter                                 | Min. | Nom. <sup>[1]</sup> | Max. | Min.   | Max.  | Unit  |

| RESISTANCE: PULSE.COM to GEN.A or GEN.B   | 9    | 30                  | 59   | 8      | 61.5  | ohms  |

| RESISTANCE: PULSE.COM to REP.A or REP.B   | 9    | 20                  | 26   | 8      | 27    | ohms  |

| RESISTANCE: PULSE.COM to SWAP.A or SWAP.B | 44   | 100                 | 149  | 40     | 155.5 | ohms  |

| RESISTANCE: PULSE.COM to BOOT.REP         | 3.5  | 8                   | 24   | 3      | 25    | ohms  |

| RESISTANCE: PULSE.COM to BOOT.SWAP        | 5    | 15                  | 36   | 4.5    | 37.5  | ohms  |

| RESISTANCE: DET.OUT A+ to DET.OUT.A-      | 670  | 1030                | 1903 | 620    | 1984  | ohms  |

| RESISTANCE: DET.OUT B+ to DET.OUT B-      | 670  | 1030                | 1903 | 620    | 1984  | ohms  |

| RESISTANCE: DET.COM to DET.SUPPLY         | 355  | 600                 | 1050 | 338    | 1095  | ohms  |

| X.COIL RESISTANCE                         |      | 4.6                 |      | 329    |       | ohms  |

| Y.COIL RESISTANCE                         |      | 2.0                 |      |        |       | ohms  |

| X.COIL INDUCTANCE                         |      | 97                  |      |        |       | μН    |

| Y.COIL INDUCTANCE                         |      | 80                  |      |        |       | μН    |

| OPERATING POWER                           |      | 1.20                | 1.75 |        |       | watts |

| STANDBY POWER                             |      | 0.25                | .45  |        |       | watts |

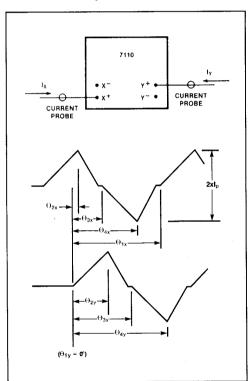

### DRIVE REQUIREMENTS CHARACTERISTICS[2] (To = Ba

| (T <sub>C</sub> = Range Specified on first page. | (Tc | =Range | Specified | on | first | page |

|--------------------------------------------------|-----|--------|-----------|----|-------|------|

|--------------------------------------------------|-----|--------|-----------|----|-------|------|

| Symbol            | Parameter                      | Min.  | Nom. <sup>[1]</sup> | Max.  | Units   |

|-------------------|--------------------------------|-------|---------------------|-------|---------|

| fR                | Field Rotation Frequency       | 49.95 | 50.000              | 50.05 | kHz     |

| lpx               | X.Coil Peak Current            |       | 600                 |       | ma      |

| l <sub>py</sub>   | Y.Coil Peak Current            |       | 750                 |       | ma      |

| θ <sub>1x</sub>   | X.Coil Positive Turn-On Phase  | 268   | 270                 | 272   | degrees |

| θ <sub>2x</sub>   | X.Coil Positive Turn-Off Phase | 16    | 18                  | 20    | degrees |

| θ <sub>3x</sub>   | X.Coil Negative Turn-On Phase  | 88    | 90                  | 92    | degrees |

| $\Theta_{4x}$     | X.Coil Negative Turn-Off Phase | 196   | 198                 | 200   | uogices |

| θ <sub>1y</sub>   | Y.Coil Positive Turn-On Phase  | 0     | 0                   | 0     | degrees |

| θ <sub>2y</sub> . | Y.Coil Positive Turn-Off Phase | 106   | 108                 | 110   | degrees |

| Өзу               | Y.Coil Negative Turn-On Phase  | 178   | 180                 | 182   | degrees |

| θ49               | Y.Coil Negative Turn-Off Phase | 286   | 288                 | 290   | degrees |

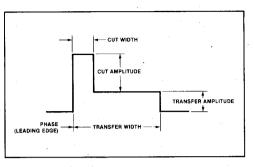

# **CONTROL PULSE REQUIREMENTS** (T<sub>C</sub> = range specified on first page)<sup>[5]</sup>

|                          | Amplitude |                    | Pulse of Leading Edge<br>(Degrees) <sup>[3]</sup> |           |                        | Width<br>(Degrees) <sup>[3]</sup> |      |         |     |

|--------------------------|-----------|--------------------|---------------------------------------------------|-----------|------------------------|-----------------------------------|------|---------|-----|

| Pulse                    | Min.      | Nom <sup>[1]</sup> | Max.                                              | Min.      | Nom.[1]                | Max.                              | Min. | Nom.[1] | Max |

| GEN.A, GEN.B CUT         | 62        | 75                 | 81                                                | 266<br>86 | 270 (Odd)<br>90 (Even) | 274<br>94                         | 3    | 6.75    | 8   |

| GEN.A, GEN.B TRANSFER    | 34        | 40                 | 49                                                | 266<br>86 | 270 (Odd)<br>90 (Even) | 274<br>94                         | 86   | 90      | 94  |

| REP.A, REP.B CUT         | 170       | 200                | 240                                               | 268       | 270                    | 277                               | 3    | 6.75    | 8   |

| REP.A, REP.B TRANSFER    | 126       | 145                | 160                                               | 268       | 270                    | 277                               | 86   | 90      | 94  |

| SWAP                     | 111       | 125                | 134                                               | 176       | 180                    | 184                               | 513  | 517     | 521 |

| BOOT.REP CUT             | 85        | 100                | 110                                               | 268       | 270                    | 277                               | 3    | 6.75    | 8   |

| BOOT.REP TRANSFER        | 63        | 75                 | 80                                                | 268       | 270                    | 277                               | 86   | 90      | 94  |

| BOOT.SWAP <sup>[4]</sup> | 63        | 75                 | 80                                                | 176       | 180                    | 184                               |      | 360     | 94  |

#### NOTES:

- 1. Nominal values are measured at  $T_C = 25^{\circ}C$ .

- 2. See Fig. 6 for test setup and X-Y coil waveforms.

- Pulse timing is given in terms of the pulse relations as shown in Figure 7. For example, a 7110 operating at f<sub>R</sub>=50 kHz would have a REPA transfer width of 90° which is 5 μs.

- Boot.Swap is not normally accessed during operation. It is utilitized at the factory to write the index address and redundant loop information onto the bootstrap loops before shipment.

- 5. 7110-5 is sold only as a matched part with the 7230-5. Matched parts are tested over temperature range for  $V_{DD} = 12V \pm 5\%$ .

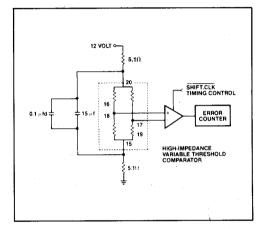

### **OUTPUT CHARACTERISTICS**

| Symbol         | Min. <sup>[2]</sup> | Nom. <sup>[1]</sup> | Max. <sup>[2]</sup> | Units | Test<br>Conditions  |

|----------------|---------------------|---------------------|---------------------|-------|---------------------|

| S <sub>1</sub> | 2.7                 | 6                   |                     | mV    | See<br>notes 1, 2,3 |

| S <sub>0</sub> |                     | 1                   | 2.3                 | mV    | 110(63 1, 2,0       |

#### NOTES:

- 1. Nominal values are measured at T<sub>C</sub>=25°C.

- Min/Max. values for S<sub>1</sub>/S<sub>0</sub> are measured at worst case conditions and tested to a system error rate of 10<sup>-9</sup> when used with the 7242 formatter sense amplifier without ECC enabled.

- See Fig. 8 for test setup, and Fig. 9 for detector output waveforms and timing.

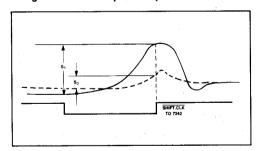

Figure 6. X-Y Coil Waveforms

Figure 7. Control Pulse Waveform

Figure 8. Test Setup for Output Measurement

Figure 9. Detector Output Waveforms

INTEL CORPORATION, 3065 Bowers Avenue, Santa Clara, CA 95051 (408) 987-8080

Printed in U.S.A./Q-90/11-82/15K/JR/JT